Engineering Software

Overview

Low Cost, Low Power, Fast: The accepted design methodology of synthesis, standard cell route, and static analysis imposes limits on the design approach. By using a semi-custom methodology, the design can be optimized for speed, power and cost. An optimized design will reduce transitions, reduce capacitance, and reduce transistor count. GSL seeks these advantages while minimizing the disadvantages of a custom approach. The GSL methodology requires a significant infrastructure. Existing libraries of working designs are required for selection and interactive modification. The design also requires timing characterization and margin checks. GSL can be folded into your existing methodology by implementing only sections of the full design that provide the most benefit. See ALU Description for an example design that reduces transistor counts.

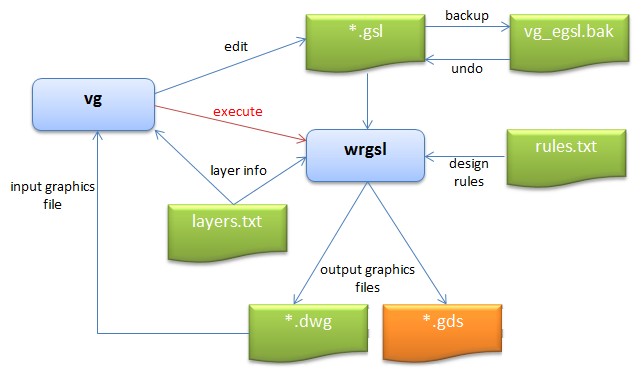

Layout: Custom cell and block layouts are drawn using the GSL design rule independent format. These

are reusable layouts that can be targeted to different rule sets. The GSL format is written to a GDS file using a

design rule file and a layers file. A graphics editor program VG views and edits GSL layouts. VG also displays layouts

directly from the GDS stream file format. CDL netlists are extracted from GSL with the diode sizes, wire capacitances and transistor sizes.

The layout is verified for systematic DRC errors and ERCs.

Layout: Custom cell and block layouts are drawn using the GSL design rule independent format. These

are reusable layouts that can be targeted to different rule sets. The GSL format is written to a GDS file using a

design rule file and a layers file. A graphics editor program VG views and edits GSL layouts. VG also displays layouts

directly from the GDS stream file format. CDL netlists are extracted from GSL with the diode sizes, wire capacitances and transistor sizes.

The layout is verified for systematic DRC errors and ERCs.

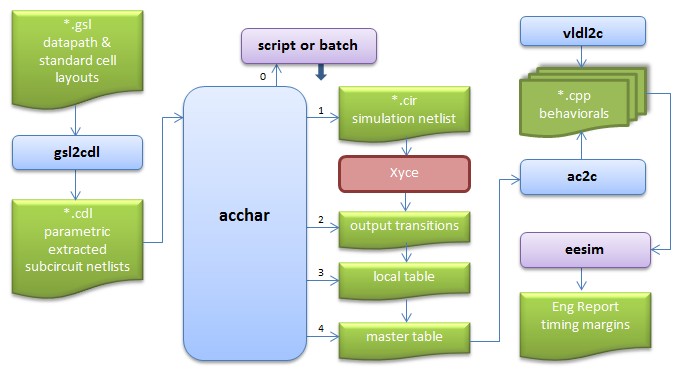

Characterization: Timing characterization of the cells is conveniently processed on a PC (with bsim3 models) interfacing to

the Xyce simulator or HSpice. It also runs in Linux. The simulation data is collected into tables and then inserted into the simulation primitives.

The timing parameters are characterized to the desired resolution and provided to the simulator so that the timing

margins are recorded during the simulation of the functional test pattern.

Characterization: Timing characterization of the cells is conveniently processed on a PC (with bsim3 models) interfacing to

the Xyce simulator or HSpice. It also runs in Linux. The simulation data is collected into tables and then inserted into the simulation primitives.

The timing parameters are characterized to the desired resolution and provided to the simulator so that the timing

margins are recorded during the simulation of the functional test pattern.

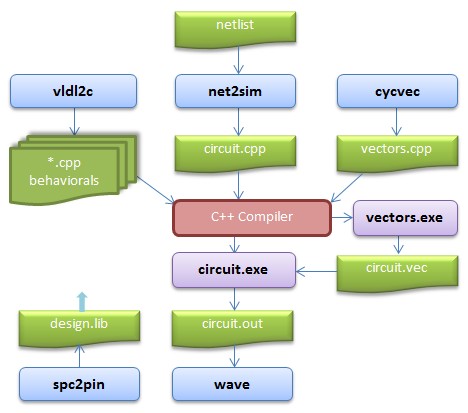

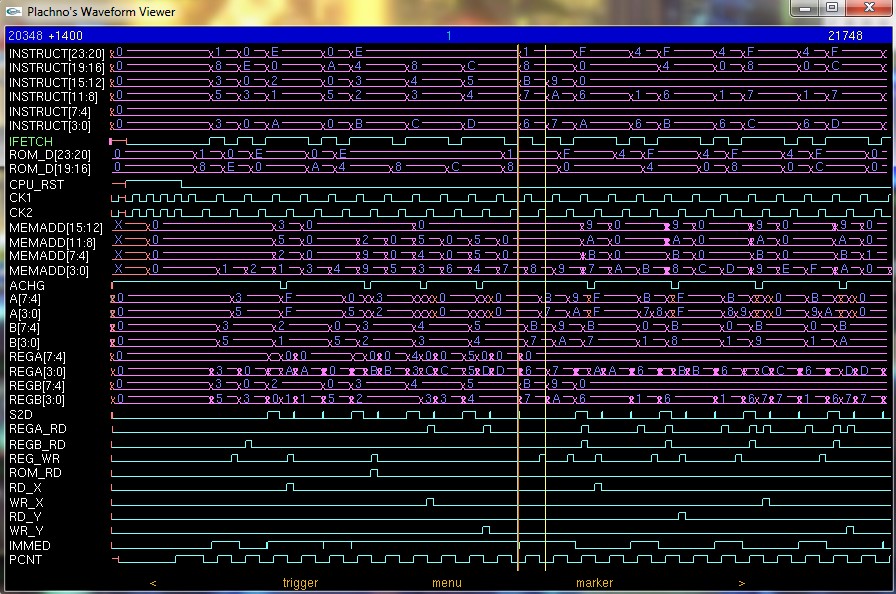

Simulation: EESIM is a compiled event driven simulator that utilizes C++ behaviorals. VLDL2C creates the C++

behaviorals for the design library. The designs can be simulated at switch level (sized transistor), gate level (for

timing margins), and behavioral level (C++). The switch level input can be a standard Spice netlist. The simulator

automatically provides an internal timing model in the absence of back-annotated data. EESIM will output an

engineering report that records the design margins for the test pattern. Cycle based vectors are created

using the CYCVEC code. The output waveforms are displayed by the WAVE program using the interactive Fat-Finger GUI.

Simulation: EESIM is a compiled event driven simulator that utilizes C++ behaviorals. VLDL2C creates the C++

behaviorals for the design library. The designs can be simulated at switch level (sized transistor), gate level (for

timing margins), and behavioral level (C++). The switch level input can be a standard Spice netlist. The simulator

automatically provides an internal timing model in the absence of back-annotated data. EESIM will output an

engineering report that records the design margins for the test pattern. Cycle based vectors are created

using the CYCVEC code. The output waveforms are displayed by the WAVE program using the interactive Fat-Finger GUI.

Interactive Graphics CAD/CAE Software

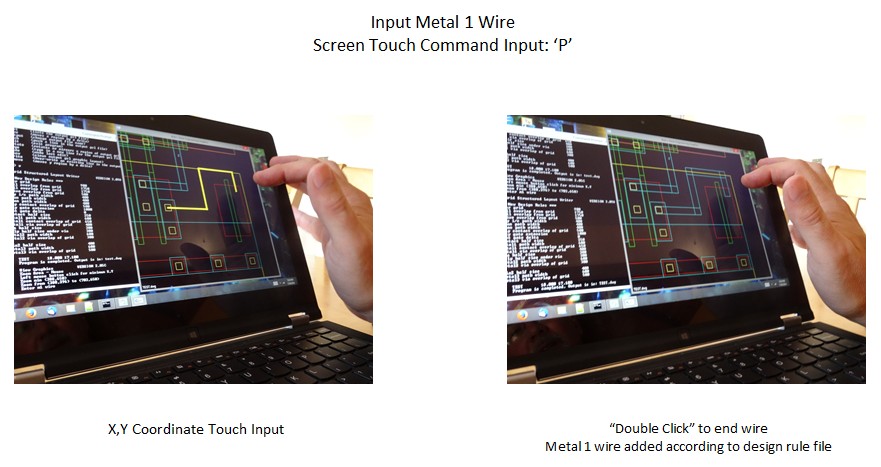

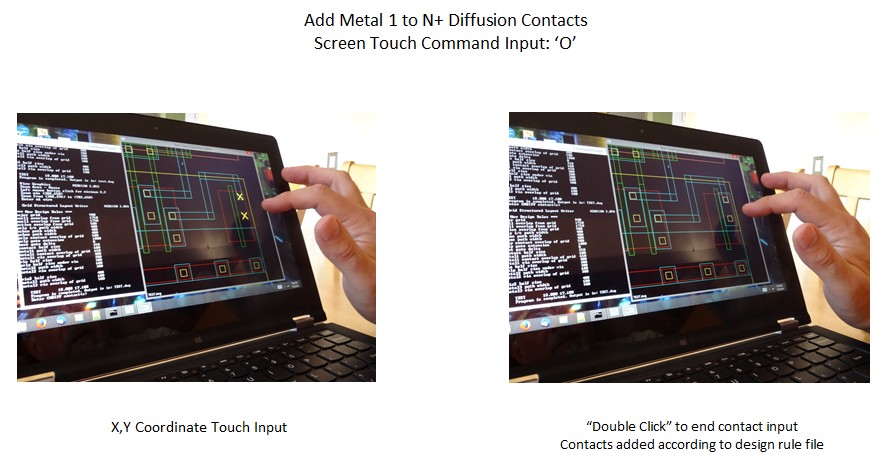

The software shown above and below is both a GDSII viewer and a GSL editor. I wrote this program using the MS Visual Studio C++ compiler and it uses the OpenGL graphics format. The goals of this program is to have a very small memory footprint, to execute fast, and to have a practical straightforward user interface. There is no "stream-in" process required since the program reads the GDSII stream file directly. I have added touch screen command input for editing the GSL design rule independent format. This software can be used on a tablet without requiring either a keyboard or a mouse (user's preference). User command events can be invoked through touch screen character recognition or the menu can be invoked by a corner swipe or the user can continue to use the mouse and keyboard (if available). Fat-Finger event inputs (touch screen, keyboard, mouse) are independently mapped to any command delegate. Since GSL uses a major grid, it is practical to input X,Y coordinates with your finger tip. Swipes (to move a magnified view) can be embedded within any data entry command.

A very different program is the "Stream File Streaming EDitor". Unlike the interactive viewer/editor, sfsed was purposely written to be invoked inside scripts that manipulate GDSII files. This program is very useful for converting custom layouts to a new process technology. While you can use a DRC program for this function, sfsed has fast execution and retains the original layout hierarchy.

This program modifies a GDSII database performing various operations on single or multiple layers while retaining the hierarchy. This is a command line batch program similar to the SED utility in Linux. The layout engineer runs it from a script file multiple times to do all of the required edits. You can copy, move, delete, re-size individual layers, rename cells and modify text. You can also scale (magnify), snap-to-grid and translate every layer in the database.

Download the Windows sfsed program with any related files (zip file)

EESIM

EESIM is a logic simulator for integrated circuit design. Specifically, it is a event driven

logic simulator that handles a mixture of logic gates, transistors, and behaviorals for

a circuit design methodology of custom datapath with routed control. It is a

dynamic timing analyzer in the sense that EESIM outputs an engineering report

with worst case timing margins found during the simulation pattern and

other useful design information. The timing model is an integral part of the

simulator. EESIM is a compiled simulator so it has fast simulation

executions.

Examples of the items listed in the engineering report are the AC current dissipation, toggle test, worst case driven nodes, worst set-up time margins, worst hold time margins, worst min pulse widths, worst removal times, etc. The user can specify how many instances of each test are retained, sorted and printed out.

Included with the logic simulator are several other functions required for integrated circuit design. This includes:

EESIM

The logic simulator works from a Spice or a Blocks input netlist. EESIM has an interactive mode for debugging the design. Transistor level spice format netlist lines can be intermixed with the gate level netlist and simulated at the switch level using an "Rsim-like" timing model.

Primitive Generation

Simulation primitives can be quickly generated using the VLDL syntax. This is used to create the simulation library for standard cells or datapath cells. This program will automatically insert the required timing checks into the flip-flop and latch primitives for the EESIM engineering report.

Waveform Viewer

The output logic waveforms are viewed graphically and plots can be printed out.

Timing Delay Characterization

Spice simulations are automated for the cell level timing characterizations. These simulated timing values are then updated into the logic primitive library. This program differs from other commercially available programs in that multiple groups of similar standard cell types are simulated and characterized at the same time. Human interaction is kept to a minimum.

Test Vector Creation

The engineer can write cycle based functional test vectors for the simulations.

Cell Layouts

Design rule independent GDSII format cell layout generation.

Design Rule Independent Layout Generator

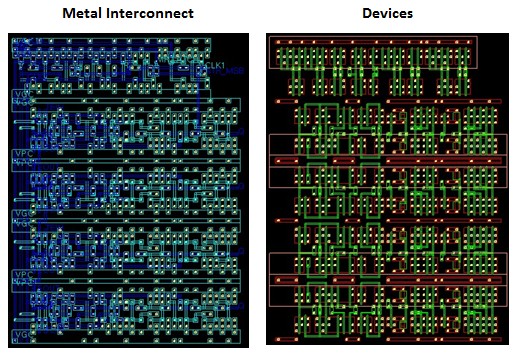

Shown to the left is a GSL generated layout. This is the most speed critical circuit for the

control of a high speed serial receiver.

Shown to the left is a GSL generated layout. This is the most speed critical circuit for the

control of a high speed serial receiver.

Grid Structured Layout or GSL is a technique for generating design rule independent layouts. The physical layout is created in GSL format and then a program called wrgsl reads a design rule file and generates a DRC clean GDSII database. Numerous standard cell libraries (400 to 600 cells per library) exist in GSL format. I have also generated a small processor datapath in GSL and some of the smaller memories (as well as the standard cells) in the ESS PC audio product were done in GSL. These layouts were manufactured in high volume with excellent yields.

Interactive GSL layout edits can be done using the vg program. Netlists are generated from the GSL format with extracted wire capacitance and diode area/perimeters since the layout topology is defined. The wrgsl program can be run either on a PC or on a Linux workstation (the same is true for almost all of my programs).

I have also found that the front end of the wrgsl program is very useful for determining scaling factors for moving custom (non-GSL) layouts between different processes. The grid values are proportional to the best scaling factor possible without generating DRC errors.

Reverse Engineering Software

I have written a set of C programs to help automate the reverse engineering of integrated circuits. This includes:

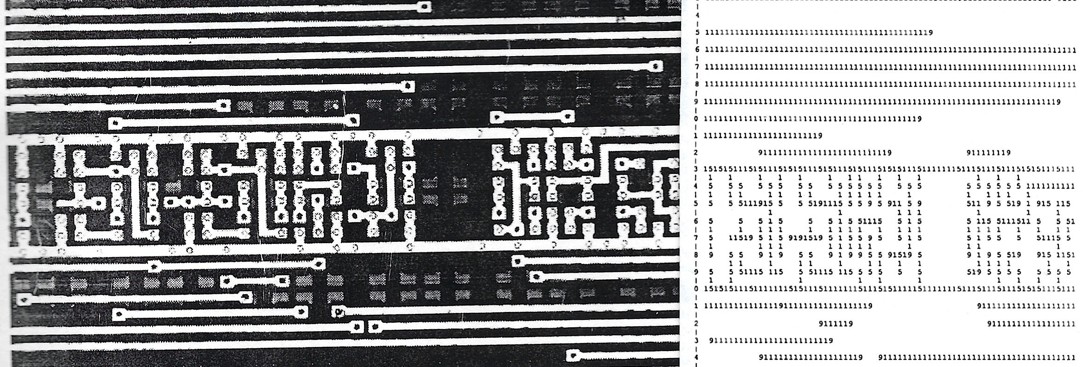

- An image processing program that reads a series of commands and performs various functions on the scanned bitmaps to clean up the database from flaws in the etching and the scanning process.

- Bitmap to GDSII conversion.

- Grouping of transistors into cells which includes algorithmic and library matching for cell identification.

- Connectivity tracing of wires in the GDSII database to create a gate level netlist.

- ERC error identification and the creation of smaller databases to trace and fix scanning errors (the full database is too big for Cadence).

- Blocking and higher level description translation of the netlist.

On the right in the above photo is an internal representation from the "bitmap.c" program that converts a scanned bitmap image (co-focal laser) to GDSII polygon format (May 1991). The program reads a user written command file to perform sequenced image processing functions. After image clean-up, the metal 1 (the 1's in the figure on the right), contacts (the 5's), and vias (the 9's) are identified and then output in GDSII format. This is just one early step in the reverse engineering C programs that I wrote. All code is orignal and does not use external libraries.

Other Engineering Software

I have written many other engineering programs in C++/C including:

- Block level layout compilers. This includes several layout compilers for analog filters that required design rule independent layout for cell placement/connection and filter coefficient programming using sized resistors or capacitors.

- I wrote the back-annotation program used on the PC-audio products at ESS. This was a major program that calculated all of the gate delays externally to the simulator using the router wire lengths and then back-annotated the per instance pin-to-pin delay values. This was also used for "management by software" in that the database is searched for marginal design issues and the engineers were required to sign off on them before tape out.

- I always write the assemblers for the processors I design. For the RP, it is a cross-assembler in that the original Zilog Z8 source code is translated directly into the RP RISC code (sometimes requiring multiple instructions). Even with that there was only a 15% premium over the original CISC code size.

- I wrote a graphical to netlist generator for both Valid and Orcad schematics.

- I wrote many netlist translators including one set-up to allow an engineer to use Berkeley misII (synthesis) to do an early RTL design flow. I presently use Berkeley ABC for synthesis from VLDL format.

- As well as ROM programmers, static timing analysis, ATE vector translation, bmod simulator, etc.

Application Program Licensing

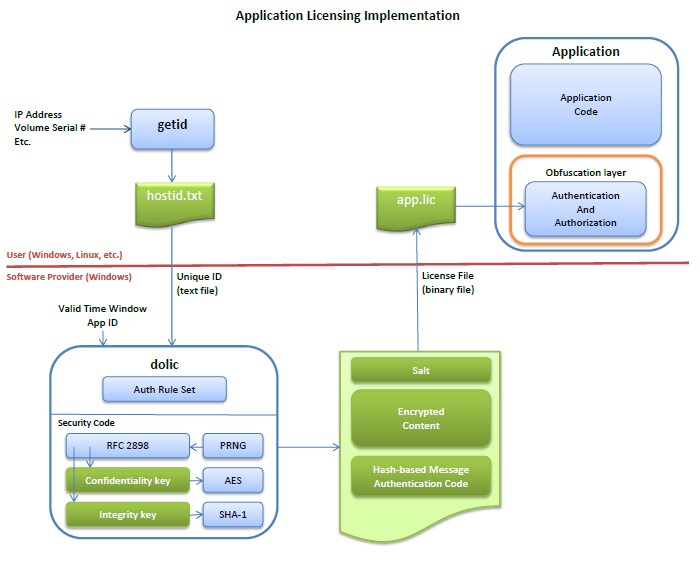

Some years ago I developed a method for licensing application software. The present implementation has AES

encryption on the license file as shown on the left. The license file contains the Salt, Encrypted Content and a Hash-based

Message Authentication Code. RFC 2898 is used for the Confidentiality key and the Integrity key generation.

Some years ago I developed a method for licensing application software. The present implementation has AES

encryption on the license file as shown on the left. The license file contains the Salt, Encrypted Content and a Hash-based

Message Authentication Code. RFC 2898 is used for the Confidentiality key and the Integrity key generation.

On a Windows platform an unique ID is created from machine resources including the IP address, the disk volume serial number, and several other items. Linux platforms use the existing hostid. The user can email the generated ID or attach the created text file for the license. A license file is written that ties the software to the user's specific computer and also restricts the usage within a valid time window. The generated binary license file can be emailed back to the user.

This implementation uses standard security practices for AES encryption and authentication. Authentication is required to ensure that the license file as not been manipulated or compromised. An obfuscation layer is used inside the application program to impede disassembly reverse attempts.

Archiving Software

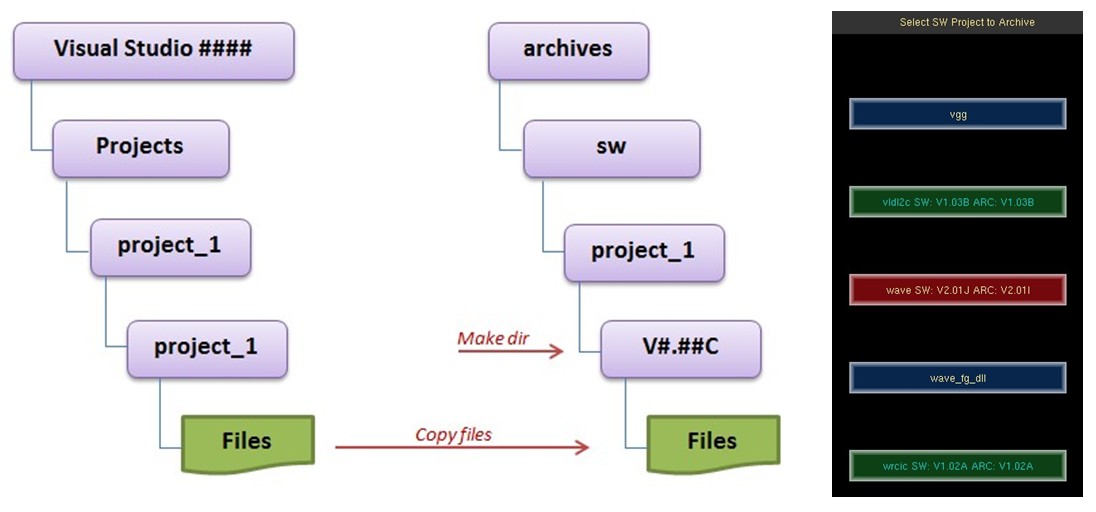

The task of manual archiving can be error prone. Updating to the latest software library versions can be inadvertenly overlooked. The benefit

of the ARC software is automatically determining and comparing the versions of each software file. ARC provides a thorough list for

the software versions of each file used in the project. The available operations are then color coded for user selection. Software projects,

web site HTML and documents can be archived. A Change List file documenting the revisions between versions is automatically (zero mouse clicks)

written for every software project archive operation. Software toolkit versions (reusable classes) are managed by their version numbers across

multiple programs. Program releases and local installs are also managed. The ARC program also performs batch backups to external drives.

The task of manual archiving can be error prone. Updating to the latest software library versions can be inadvertenly overlooked. The benefit

of the ARC software is automatically determining and comparing the versions of each software file. ARC provides a thorough list for

the software versions of each file used in the project. The available operations are then color coded for user selection. Software projects,

web site HTML and documents can be archived. A Change List file documenting the revisions between versions is automatically (zero mouse clicks)

written for every software project archive operation. Software toolkit versions (reusable classes) are managed by their version numbers across

multiple programs. Program releases and local installs are also managed. The ARC program also performs batch backups to external drives.